1. Y broblem oedi

O dan yr un amledd craidd, mae amledd gweithredu gwirioneddol DDR2 ddwywaith yn fwy na DDR. Mae hyn oherwydd y ffaith bod gan gof DDR2 ddwywaith y gallu cyn-ddarllen 4BIT o gof DDR safonol. Mewn geiriau eraill, er bod DDR2, fel DDR, yn defnyddio'r dull sylfaenol o drosglwyddo data ar yr un pryd ag oedi codiad y cloc ac oedi cwympo, mae gan DDR2 ddwywaith allu DDR i ddarllen data gorchymyn system ymlaen llaw. Mewn geiriau eraill, o dan yr un amledd gweithredu o 100MHz, amledd gwirioneddol DDR yw 200MHz, tra gall DDR2 gyrraedd 400MHz.

Yn y modd hwn, mae problem arall yn codi: yng nghof DDR a DDR2 gyda'r un amledd gweithredu, mae hwyrni cof yr olaf yn arafach na'r cyntaf. Er enghraifft, mae gan DDR 200 a DDR2-400 yr un oedi, tra bod gan yr olaf ddwywaith y lled band. Mewn gwirionedd, mae gan DDR2-400 a DDR 400 yr un lled band, maent ill dau yn 3.2GB / s, ond amledd gweithredu craidd DDR400 yw 200MHz, ac amledd gweithredu craidd DDR2-400 yw 100MHz, sy'n golygu oedi DDR2 -400 Mae'n uwch na DDR400.

2. Pecynnu a chynhyrchu gwres

Y datblygiad arloesol mwyaf o dechnoleg cof DDR2 mewn gwirionedd yw nad yw defnyddwyr yn meddwl ddwywaith gallu trosglwyddo DDR, ond gyda chynhyrchu gwres is a defnydd pŵer is, gall DDR2 sicrhau cynnydd amledd cyflymach a datblygiadau arloesol. Y terfyn 400MHZ o DDR safonol.

Mae cof DDR fel arfer yn cael ei becynnu mewn sglodyn TSOP. Gall y pecyn hwn weithio'n dda ar 200MHz. Pan fydd yr amledd yn uwch, bydd ei binnau hir yn cynhyrchu rhwystriant uchel a chynhwysedd parasitig, a fydd yn effeithio ar ei berfformiad. Anhawster sefydlogrwydd a gwella amledd. Dyma pam ei bod yn anodd i amledd craidd DDR dorri trwy 275MHZ. Ac mae cof DDR2 yn mabwysiadu ffurflen pecyn FBGA. Yn wahanol i'r pecyn TSOP a ddefnyddir yn helaeth ar hyn o bryd, mae pecyn FBGA yn darparu gwell perfformiad trydanol a afradu gwres, sy'n darparu gwarant da ar gyfer gweithrediad sefydlog cof DDR2 a datblygu amleddau yn y dyfodol.

Mae cof DDR2 yn defnyddio foltedd 1.8V, sy'n llawer is na safon DDR 2.5V, gan ddarparu defnydd pŵer sylweddol llai a llai o wres. Mae'r newid hwn yn sylweddol.

Yn ychwanegol at y gwahaniaethau a grybwyllwyd uchod, mae DDR2 hefyd yn cyflwyno tair technoleg newydd, sef OCD, ODT ac Post CAS.

① OCD (Gyrrwr Oddi Sglodion): Dyma'r addasiad gyrrwr all-lein, fel y'i gelwir. Gall DDR II wella cyfanrwydd signal trwy OCD. Mae DDR II yn addasu'r gwerth gwrthiant tynnu i fyny / tynnu i lawr i wneud y ddwy foltedd yn gyfartal. Defnyddiwch OCD i wella cyfanrwydd signal trwy leihau gogwydd DQ-DQS; gwella ansawdd signal trwy reoli foltedd.

② ODT: ODT yw gwrthydd terfynu'r craidd adeiledig. Rydym yn gwybod bod angen nifer fawr o wrthyddion terfynu ar y motherboard gan ddefnyddio DDR SDRAM er mwyn atal terfynell y llinell ddata rhag adlewyrchu signalau. Mae'n cynyddu cost gweithgynhyrchu'r motherboard yn fawr. Mewn gwirionedd, mae gan wahanol fodiwlau cof ofynion gwahanol ar gyfer y gylched derfynu. Mae maint y gwrthydd terfynu yn pennu cymhareb signal ac adlewyrchiad y llinell ddata. Os yw'r gwrthiant terfynu yn fach, mae adlewyrchiad signal y llinell ddata yn isel ond mae'r gymhareb signal-i-sŵn hefyd yn isel; Os yw'r gwrthiant terfynu yn uchel, bydd cymhareb signal-i-sŵn y llinell ddata yn uchel, ond bydd adlewyrchiad y signal hefyd yn cynyddu. Felly, ni all y gwrthiant terfynu ar y motherboard gyd-fynd â'r modiwl cof yn dda iawn, a bydd yn effeithio ar ansawdd y signal i raddau. Gall DDR2 gynnwys gwrthyddion terfynu addas yn ôl ei nodweddion ei hun, er mwyn sicrhau'r donffurf signal orau. Gall defnyddio DDR2 nid yn unig leihau cost y motherboard, ond hefyd gael yr ansawdd signal gorau, sydd heb ei gyfateb gan DDR.

③ Post CAS: Disgwylir iddo wella effeithlonrwydd defnyddio cof DDR II. Mewn gweithrediad Ôl CAS, gellir mewnosod y signal CAS (darllen / ysgrifennu / gorchymyn) un cylch cloc ar ôl y signal RAS, a gall gorchymyn CAS aros yn ddilys ar ôl yr oedi ychwanegol (Ychwanegiad Ychwanegol). Mae'r tRCD gwreiddiol (RAS i CAS ac oedi) yn cael ei ddisodli gan AL (Additive Latency), y gellir ei osod yn 0, 1, 2, 3, 4. Gan fod y signal CAS yn cael ei osod un cylch cloc ar ôl y signal RAS, mae'r ACT ac ni fydd signalau CAS byth yn gwrthdaro.

Yn gyffredinol, mae DDR2 yn defnyddio llawer o dechnolegau newydd i wella llawer o ddiffygion DDR. Er bod ganddo lawer o ddiffygion ar hyn o bryd o ran cost uchel a hwyrni araf, credir, gyda gwelliant a gwelliant parhaus technoleg, y bydd y problemau hyn yn cael eu datrys yn y pen draw.

(1) manylebau technegol DDR2

Bydd amledd cychwyn cof DDR2 yn cychwyn o 400Mhz, amledd safonol uchaf cof DDR. Mae'r amleddau y gellir eu cynhyrchu bellach wedi'u diffinio i gefnogi 533Mhz i 667Mhz. Yr amledd gweithredu safonol yw 200/266 / 333MHz, a'r foltedd gweithredu yw 1.8V. Mae DDR2 yn defnyddio'r safon rhyngwyneb 240 PIN DIMM sydd newydd ei diffinio, sy'n gwbl anghydnaws â safon rhyngwyneb DIMM DDR 184PIN presennol. Mae hyn yn golygu na all yr holl famfyrddau presennol sydd â rhyngwynebau safonol DDR ddefnyddio cof DDR2. Bydd hyn yn dod yn rhwystr mawr i boblogeiddio safonau cof DDR2. Yn ffodus, bydd platfform cenhedlaeth nesaf INTEL yn cefnogi rhyngwyneb 240PIN DDR2 yn llawn, gan osod y sylfaen ar gyfer poblogeiddio DDR2 yn 2005.

Rwy'n credu bod pawb eisoes wedi gweld bod amrywiaeth o gynhyrchion cardiau graffeg sy'n defnyddio cof DDR2 wedi'u lansio ar y farchnad. Fodd bynnag, mae safonau cynhyrchu a dulliau cof DDR2 a ddefnyddir ar gardiau graffeg yn hollol wahanol i'r dechnoleg DDR2 a ddefnyddir ar gymwysiadau system bwrdd gwaith. Ni fydd yr erthygl hon yn gwneud gwahaniaeth manwl am y tro, ond dylai pawb fod yn glir pam mae nifer fawr o gymwysiadau eisoes ar gael ar gardiau graffeg ond nid yw systemau bwrdd gwaith.

O'i gymharu â'r genhedlaeth flaenorol o dechnoleg DDR safonol, mae technoleg cof DDR2 yn defnyddio ffordd syml a chlir. Er bod DDR2, fel DDR, yn defnyddio'r dull sylfaenol o drosglwyddo data ar yr un pryd ag oedi codiad y cloc ac oedi cwympo, y gwahaniaeth mwyaf yw bod DDR2 Gall y cof berfformio cyn-ddarllen 4bit. Ddwywaith y cyn-ddarllen 2BIT o gof DDR safonol, sy'n golygu bod gan DDR2 ddwywaith y gallu i ddata gorchymyn system cyn-ddarllen. Rwyf wedi deall yr hyn yr wyf yn meddwl, am y rheswm hwn, yn syml, mae DDR2 yn sicrhau'r gallu trosglwyddo data cyflawn ddwywaith yn fwy na DDR. Felly mae'r awdur yn dweud wrthych fod DDR2 400Mhz hefyd wedi'i enwi'n PC3200, daliwch ati i ddarllen, pam?

Nid pwynt torri mwyaf technoleg cof DDR2 mewn gwirionedd yw'r gallu trosglwyddo y mae'r beirniaid yn credu sydd ddwywaith yn fwy na DDR, ond yn hytrach, mae'n cyflawni cynnydd amledd cyflymach gyda chynhyrchu gwres is a defnydd pŵer is. Torri trwy'r terfyn 400MHZ o DDR safonol. Mae'n ymddangos bod hyn yn ymddangos yn fwy hudol, gan dorri'r terfyn amledd uchaf, a hyd yn oed leihau cynhyrchu gwres a defnyddio pŵer? Er bod technoleg DDR2 hefyd yn defnyddio sawl technoleg newydd i gyflawni'r galluoedd uchod, mae'r allwedd yn gorwedd yng ngallu cyn-ddarllen 4BIT. Bydd yr awdur yn mynd â chi gam wrth gam.

(2) Amledd a lled band DDR2

Yn ychwanegol at amlder a lled band y tair safon cof DDR2 a ryddhawyd, mae'n werth nodi bod gan DDR2 400Mhz a DDR400Mhz yr un lled band o 3.2GB. Hefyd, gyda chymorth technoleg cof dwy-sianel, bydd 667MHZ DDR2 yn darparu lled band anhygoel o hyd at 10.6GB / S!

Capasiti cychwynnol cof DDR2 yw 256MB, hyd at 512MB, 1G. Mae'n darparu gwarant capasiti digonol ar y system bwrdd gwaith. Yn ddamcaniaethol, gall nodweddion dwysedd uchel gronynnau cof DDR2 gynnal capasiti uchaf o 4G ac uwch, a ddefnyddir yn helaeth mewn meysydd proffesiynol. Efallai y bydd hyd yn oed yn dod â gallu uwch ar lefel nGB i systemau PC yn ystod yr ychydig flynyddoedd nesaf.

Mae safon DDR2 yn nodi bod holl atgofion DDR2 yn cael eu pecynnu yn FBGA. Yn wahanol i'r TSOP a ddefnyddir yn helaeth ach pecynnau TSOP-II, mae pecyn FBGA yn darparu gwell perfformiad trydanol a afradu gwres, sy'n darparu gwarant da ar gyfer gweithrediad sefydlog cof DDR2 a datblygu amleddau yn y dyfodol. Ar hyn o bryd, defnyddir yr holl ronynnau cof DDR2 ar y cerdyn graffeg yn y modd pecyn FBGA. Mae cof DDR2 yn defnyddio foltedd 1.8V, sy'n llawer is na safon DDR 2.5V, ac felly'n darparu defnydd pŵer sylweddol llai a llai o wres. Mae'r newid hwn yn sylweddol, ac mae hefyd yn caniatáu DDR2 Mae'r cof yn fwy addas ar gyfer llyfrau nodiadau a gliniaduron. Gan y gall weithio ar foltedd mor isel, sut y gellir cyflawni'r cynnydd amledd?

(3) Egwyddor gweithio DDR2

Fel y gŵyr pawb, rhennir camau gweithio sylfaenol y cof yn: data cyn-ddarllen o'r system → arbed yng nghiw'r uned gof → trosglwyddo i'r byffer cof I / O → trosglwyddo i'r system CPU i'w brosesu.

Mae cof DDR yn defnyddio amledd craidd o 200MHZ, sy'n cael ei drosglwyddo'n gydamserol i'r storfa I / O trwy ddau lwybr, a dyma'r amledd gwirioneddol i gyflawni 400MHZ.

Mae DDR2 yn defnyddio amledd craidd o 100MHZ, sy'n cael ei drosglwyddo'n gydamserol i'r byffer I / O trwy bedwar llwybr trosglwyddo, ac mae hefyd yn cyflawni amledd gwirioneddol o 400MHZ.

Mae'r ynad clyfar eisoes wedi gweld y dirgelwch. Mae hyn yn union oherwydd y gall DDR2 ddarllen data 4BIT ymlaen llaw, gall ddefnyddio trosglwyddiad pedair ffordd, ac oherwydd mai dim ond data 2BIT y gall DDR ei ddarllen ymlaen llaw, dim ond dwy linell drosglwyddo 200MHZ y gall eu defnyddio i gyflawni 400MHZ. Yn y modd hwn, gall DDR2 leihau'r amledd craidd yn llwyr i 100MHZ heb leihau cyfanswm yr amledd, fel y gall gyflawni afradu gwres llai a gofynion foltedd is yn hawdd. Ar ben hynny, gellir cynyddu'r amledd craidd ymhellach i gyflawni 133 * 4, 166 * 4, ac uchafswm o 200 * 4 i gyrraedd 800MHZ. Fodd bynnag, mae pawb yn gwybod y gall hwyrni cof is ddod â pherfformiad uwch. Yna, yn DDR2, er mwyn sicrhau sefydlogrwydd a llyfnder trosglwyddo 4 sianel ac osgoi ymyrraeth drydanol a gwrthdaro data, defnyddir cof ychydig yn fwy na DDR. Oedi gosodiad. Rwy'n credu y gall beirniaid craff hefyd weld mai dyluniad pellgyrhaeddol yw hwn mewn gwirionedd.

(4) Technoleg nodwedd newydd DDR2

Ar ôl deall egwyddorion technegol DDR II, gadewch i ni edrych ar dair prif nodwedd newydd DDR II: OCD, ODT ac Post CAS ydyn nhw.

OCD (Gyrrwr Oddi Sglodion), also a elwir yn addasiad gyriant all-lein, gall DDR II wella cyfanrwydd signal trwy OCD. Mae DDR II yn addasu'r gwerth gwrthiant tynnu i fyny / tynnu i lawr i wneud y ddwy foltedd yn gyfartal. Hynny yw, Tynnu i fyny = Tynnu i lawr. Defnyddiwch OCD i wella cyfanrwydd signal trwy leihau gogwydd DQ-DQS; gwella ansawdd signal trwy reoli foltedd.

Mae ODT yn wrthydd terfynu ar gyfer y craidd adeiledig. Rydym yn gwybod bod angen nifer fawr o wrthyddion terfynu ar famfyrddau gan ddefnyddio DDR I SDRAM, mae angen o leiaf un gwrthydd terfynu ar gyfer pob llinell ddata, nad yw'n gost fach i'r famfwrdd. Y defnydd o wrthyddion terfynu ar y llinell signal yw atal terfynell y llinell ddata rhag adlewyrchu signalau, felly mae angen gwrthydd terfynu â gwrthiant penodol. Mae'r gwrthiant hwn yn rhy fawr neu'n rhy fach. Mae cymhareb signal-i-sŵn y gylched â gwrthiant mwy yn uwch ond mae'r adlewyrchiad signal yn fwy difrifol. Gall gwrthiant bach leihau adlewyrchiad y signal ond bydd yn achosi i'r gymhareb signal-i-sŵn ostwng. Yn ogystal, gan efallai na fydd gan wahanol fodiwlau cof yr un gofynion gwrthsefyll terfynu yn union, mae'r motherboard hefyd yn fwy piclyd ynghylch modiwlau cof.

Mae gan DDR II wrthydd terfynu adeiledig, sy'n diffodd y gwrthydd terfynu pan fydd y gronynnau DRAM yn gweithio, ac yn troi'r gwrthydd terfynu ar gyfer gronynnau DRAM nad ydynt yn gweithio i leihau adlewyrchiad signal. Mae ODT yn dod ag o leiaf ddwy fudd i DDR II. Un yw bod dileu'r gwrthydd terfynu ar y motherboard yn lleihau cost y motherboard ac yn gwneud dyluniad y bwrdd PCB yn haws. Yr ail fantais yw y gall y gwrthydd terfynu gyd-fynd â "nodweddion" y gronynnau cof, fel bod y DRAM yn y cyflwr gorau.

Ar ôl CAS, mae ar fin gwella effeithlonrwydd defnyddio cof DDR II. Mewn gweithrediad Ôl CAS, gellir mewnosod y signal CAS (darllen / ysgrifennu / gorchymyn) un cylch cloc ar ôl y signal RAS, a gall gorchymyn CAS aros yn ddilys ar ôl yr oedi ychwanegol (Ychwanegiad Ychwanegol). Mae'r tRCD gwreiddiol (RAS i CAS ac oedi) yn cael ei ddisodli gan AL (Additive Latency), y gellir ei osod yn 0, 1, 2, 3, 4. Gan fod y signal CAS yn cael ei osod un cylch cloc ar ôl y signal RAS, mae'r ACT ac ni fydd signalau CAS byth yn gwrthdaro.

Mewn gweithrediad arferol, y paramedrau cof amrywiol ar yr adeg hon yw: tRRD = 2, tRCD = 4, CL = 4, AL = 0, BL = 4 (BL yw'r hyd data byrstio, Hyd Byrstio). Gwelwn fod tRRD (yr oedi o RAS i RAS) yn ddau gylch cloc, ac mae tRCD (yr oedi o RAS i CAS) yn bedwar cylch cloc, felly mae'r signalau ACT (actifadu segment) a CAS yn gwrthdaro ar y pedwerydd cylch cloc. , Mae ACT yn symud yn ôl gan un cylch cloc, felly gallwch weld bod cylch cloc o BUBBLE yng nghanol y trosglwyddiad data dilynol.

Gadewch i ni edrych ar weithrediad Post CAS. Y paramedrau cof ar yr adeg hon yw: tRRD = 2, tRCD = 4, CL = 4, AL = 3, BL = 4. Mae RAS wedi'i osod mewn cylch cloc ar ôl y signal ACT, felly ni fydd CAS ac ACT yn gwrthdaro, mae AL yn disodli tRCD (mewn gwirionedd, gallwch ddychmygu nad yw tRCD wedi'i leihau, ond ei fod yn newid cysyniadol, mae CAS yn mynd tuag yn ôl Un cloc beicio, ond mae AL yn fyrrach na tRCD, gellir canslo gwrthdrawiad y gorchymyn signal trwy addasu), ac mae'r DRAM yn cadw'r gorchymyn darllen yn ystod yr oedi ychwanegol. Oherwydd y dyluniad hwn, ni fydd ACT a CAS yn gwrthdaro mwyach, ac ni fydd BUBBLE yn yr amseriad darllen cof.

Bydd tri budd i ddefnyddio Post CAS ynghyd â Ychwanegol Ychwanegol:

1. Gellir canslo ffenomen y Gwrthdrawiad ar y bws gorchymyn yn hawdd

2. Gwella effeithlonrwydd y bws gorchymyn a data

3. Heb Bubble, gellir gwella lled band y cof go iawn

FSB DOTHAN cyffredin arall yw 533, sy'n golygu y gall y cof gyda DDR533 gwrdd â lled band y cof yn unig, ond dim ond DDR1 sydd gan y llyfr nodiadau cyfredol DDR400 ar y mwyaf, ac yn gyffredinol ni all 333 gwrdd â FSB DOTHAN. Ar yr adeg hon, daw'r cof yn dagfa'r system. Ar ôl i'r platfform 915 ddod allan Gall gefnogi DDR2 dwy-sianel DDR2 gan ddechrau o 400 a hyd at 533.

Ar yr adeg hon, efallai eich bod wedi darganfod y gall DDR2 533 un-sianel fodloni FSB DOTHAN yn llawn, hynny yw, mae gan DDR2 533 sianel ddeuol, dim ond FSB = 1066 CPU sy'n gallu ei gyfateb. Cyn i INTEL1066FSB U ddod allan, Gwastraff yw sianel ddeuol DDR2 533 yn y bôn, felly mae'r gwelliant perfformiad y mae sianel ddeuol DDR2 yn dod ag ef i blatfform Sonama yn fach iawn. Mae DOTHAN wedi dod yn dagfa system Sonama. Nid oes angen i ffrindiau nad ydyn nhw'n gofyn am berfformiad wario arian ar DDR2 dwy-sianel.

|

|

|

|

Pa mor bell (hir) y clawr trosglwyddydd?

Mae'r ystod trosglwyddo yn dibynnu ar nifer o ffactorau. Mae'r pellter gwir yn seiliedig ar yr antena osod uchder, ennill antena, gan ddefnyddio amgylchedd fel adeiladu a rhwystrau eraill, sensitifrwydd y derbynnydd, antena y derbynnydd. Gosod antena yn fwy uchel ac yn defnyddio yn y cefn gwlad, bydd y pellter llawer mwy yn hyn.

ENGHRAIFFT 5W FM Trosglwyddydd defnyddio yn y ddinas a'r dref enedigol:

Mae gen i UDA ddefnydd cwsmeriaid 5W trosglwyddydd fm gyda antena meddygon teulu yn ei dref enedigol, ac efe brofi 'i ag a car, ei gwmpasu 10km (6.21mile).

Rwy'n profi trosglwyddydd fm 5W gyda antena meddygon teulu yn fy nhref enedigol, mae'n cynnwys tua 2km (1.24mile).

Rwy'n profi trosglwyddydd fm 5W gyda antena meddygon teulu yn ninas Guangzhou, mae'n cynnwys tua unig 300meter (984ft).

Isod mae yr ystod fras o wahanol Trosglwyddydd pŵer FM. (Mae'r ystod yn diamedr)

0.1W ~ 5W FM Trosglwyddydd: 100M ~ 1KM

5W ~ 15W FM Ttransmitter: 1KM ~ 3KM

15W ~ 80W FM Trosglwyddydd: 3KM ~ 10KM

80W ~ 500W FM Trosglwyddydd: 10KM ~ 30KM

500W ~ 1000W FM Trosglwyddydd: 30KM ~ 50KM

1KW ~ 2KW FM Trosglwyddydd: 50KM ~ 100KM

2KW ~ 5KW FM Trosglwyddydd: 100KM ~ 150KM

5KW ~ 10KW FM Trosglwyddydd: 150KM ~ 200KM

Sut i gysylltu â ni am y trosglwyddydd?

Ffoniwch fi + 8618078869184 NEU

e-bost ataf [e-bost wedi'i warchod]

1.How bell ydych am i dalu mewn diamedr?

2.How tal ohonoch tŵr?

3.Where rydych yn dod?

A byddwn yn rhoi cyngor mwy proffesiynol i chi.

Amdanom ni

Mae FMUSER.ORG yn gwmni integreiddio'r system sy'n canolbwyntio ar offer sain / ffrydio fideo / llifo di-wifr RF a phrosesu data. Rydym yn darparu popeth o gyngor ac ymgynghoriaeth trwy integreiddio rac i osod, comisiynu a hyfforddi.

Rydym yn cynnig trosglwyddydd FM, trosglwyddydd teledu analog, trosglwyddydd teledu digidol, trosglwyddydd VHF UHF, antenâu, cysylltwyr ceblau cyfechelog, STL, ar brosesu aer, cynhyrchion darlledu ar gyfer y stiwdio, monitro arwyddol RF, offerynnau RDS, proseswyr sain ac unedau rheoli safleoedd o bell, Cynhyrchion IPTV, Fideo / Encoder Sain / Sain, wedi'u cynllunio i ddiwallu anghenion rhwydweithiau darlledu rhyngwladol mawr a gorsafoedd preifat bach fel ei gilydd.

Mae gan ein datrysiad Orsaf Radio FM / Gorsaf Deledu Analog / Gorsaf Deledu Ddigidol / Offer Stiwdio Fideo Sain / Cyswllt Trosglwyddydd Stiwdio / System Telemetreg Trosglwyddydd / System Deledu Gwesty / Darlledu Byw IPTV / Ffrydio Darlledu Byw / Cynhadledd Fideo / system Ddarlledu CATV.

Rydym yn defnyddio cynhyrchion technoleg uwch ar gyfer yr holl systemau, oherwydd gwyddom fod dibynadwyedd uchel a pherfformiad uchel mor bwysig i'r system a'r datrysiad. Ar yr un pryd mae'n rhaid i ni sicrhau hefyd bod ein system cynnyrch yn bris rhesymol iawn.

Mae gennym gwsmeriaid darlledwyr cyhoeddus a masnachol, gweithredwyr telathrebu ac awdurdodau rheoleiddio, ac rydym hefyd yn cynnig atebion a chynhyrchion i gannoedd o ddarlledwyr llai, lleol a chymunedol.

Mae FMUSER.ORG wedi bod yn allforio mwy na 15 blynedd ac mae ganddo gleientiaid ledled y byd. Gyda 13 mlynedd o brofiad yn y maes hwn, mae gennym dîm proffesiynol i ddatrys pob math o broblemau cwsmer. Gwnaethom ymrwymo i gyflenwi prisiau rhesymol iawn cynhyrchion a gwasanaethau proffesiynol. E-bost cyswllt: [e-bost wedi'i warchod]

Mae ein Ffatri

Rydym wedi moderneiddio y ffatri. Mae croeso i chi ymweld â'n ffatri pan fyddwch yn dod i Tsieina i chi.

Ar hyn o bryd, mae yna eisoes cwsmeriaid 1095 o gwmpas y byd ymweld â'n swyddfa Guangzhou Tianhe. Os byddwch yn dod i Tsieina, mae croeso i chi ymweld â ni chi.

yn Ffair

Mae hyn yn ein cyfranogiad yn 2012 Ffynonellau Global Hong Kong Electronics Ffair . Cwsmeriaid o bob cwr o'r byd yn olaf yn cael cyfle i ddod at ei gilydd.

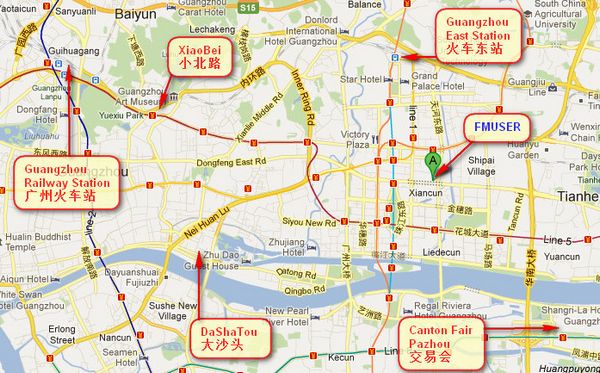

Ble mae Fmuser?

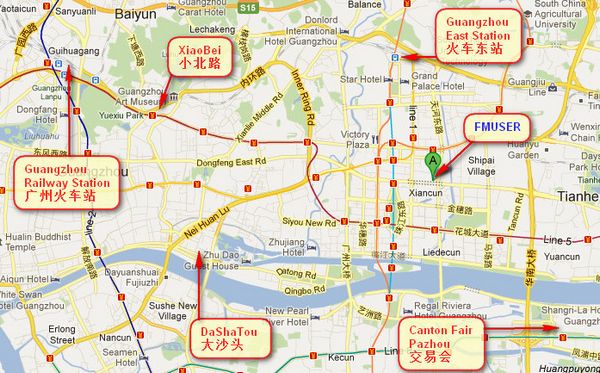

Gallwch chwilio'r rhifau hyn " 23.127460034623816,113.33224654197693 "yn google map, yna gallwch ddod o hyd i'n swyddfa fmuser.

swyddfa FMUSER Guangzhou yn Tianhe District sef y nghanol y Treganna . iawn ger i'r Ffair Treganna , gorsaf reilffordd Guangzhou, ffordd xiaobei a dashatou , Dim ond angen 10 munud os cymryd TACSI . Croeso ffrindiau o amgylch y byd i ymweld a thrafod.

Cyswllt: Sky Blue

Cellphone: + 8618078869184

WhatsApp: + 8618078869184

Wechat: + 8618078869184

E-bost: [e-bost wedi'i warchod]

QQ: 727926717

Skype: sky198710021

Cyfeiriad: Ystafell No.305 HuiLan Adeilad No.273 Road Huanpu Guangzhou Tsieina Zip: 510620

|

|

|

|

Saesneg: Rydym yn derbyn pob taliad, fel PayPal, Cerdyn Credyd, Western Union, Alipay, Archebwyr Arian, T / T, LC, DP, DA, OA, Payoneer, Os oes gennych unrhyw gwestiwn, cysylltwch â mi [e-bost wedi'i warchod] neu WhatsApp + 8618078869184

-

PayPal.  www.paypal.com www.paypal.com

Rydym yn argymell eich bod yn defnyddio Paypal i brynu ein eitemau, The Paypal yn ffordd ddiogel i'w prynu ar y rhyngrwyd.

Mae pob un o'n dudalen rhestr eitem gwaelod ar ben cael logo paypal i dalu.

Cerdyn credyd.Os nad oes gennych paypal, ond mae gennych gerdyn credyd, gallwch hefyd glicio ar y botwm Melyn PayPal i dalu gyda'ch cerdyn credyd.

-------------------------------------------------- -------------------

Ond os nad ydych wedi gerdyn credyd ac nid gennych gyfrif PayPal neu anodd ei got a accout paypal, Gallwch ddefnyddio'r canlynol:

Undeb gorllewinol.  www.westernunion.com www.westernunion.com

Talu drwy Western Union i mi:

Enw cyntaf / Enw rhybudd: Yingfeng

Enw / Cyfenw / Enw teulu: Zhang

Enw llawn: Yingfeng Zhang

Gwlad: Tsieina

City: Guangzhou

|

-------------------------------------------------- -------------------

T / T. dalu drwy T / T (trosglwyddo gwifren / Trosglwyddo telegraffig / Trosglwyddiad Banc)

GWYBODAETH BANC Gyntaf (CYFRIF CWMNI):

SWIFT BIC: BKCHHKHHXXX

Enw'r banc: BANK OF CHINA (HONG KONG) CYFYNGEDIG, HONG KONG

Cyfeiriad y Banc: BANK OF CHINA TOWER, 1 GARDEN ROAD, CENTRAL, HONG KONG

COD BANC: 012

Enw'r Cyfrif: FMUSER INTERNATIONAL GROUP LIMITED

Nifer y Cyfrif. : 012-676-2-007855-0

-------------------------------------------------- -------------------

Ail WYBODAETH BANC (CYFRIF CWMNI):

Buddiolwr: Fmuser International Group Inc.

Rhif y Cyfrif: 44050158090900000337

Banc y Buddiolwr: Cangen Guangdong Banc Adeiladu Tsieina

Cod SWIFT: PCBCCNBJGDX

Cyfeiriad: RHIF.553 Tianhe Road, Guangzhou, Guangdong, Tianhe District, China

** Sylwch: Pan drosglwyddwch arian i'n cyfrif banc, PEIDIWCH ag ysgrifennu unrhyw beth yn yr ardal sylwadau, fel arall ni fyddwn yn gallu derbyn y taliad oherwydd polisi'r llywodraeth ar fusnes masnach ryngwladol.

|

|

|

|

* Bydd yn cael ei anfon yn 1-2 diwrnod gwaith pan fydd y taliad clir.

* Byddwn yn anfon at eich cyfeiriad paypal. Os ydych am newid cyfeiriad, anfonwch eich cyfeiriad cywir a rhif ffôn i fy e-bost [e-bost wedi'i warchod]

* Os yw'r pecynnau yn is 2kg, byddwn yn cael ei gludo drwy'r post gynwys post airmail, bydd yn cymryd tua 15-25days i eich llaw.

Os yw'r pecyn yn fwy na 2kg, byddwn yn llong drwy EMS, DHL, UPS, FedEx dosbarthu cyflym gyflym, bydd yn cymryd tua 7 ~ 15days i eich llaw.

Os bydd y pecyn yn fwy na 100kg, byddwn yn anfon drwy DHL neu cludo nwyddau awyr. Bydd yn cymryd tua 3 ~ 7days i eich llaw.

Mae pob un o'r pecynnau yn cael eu ffurflen Tsieina Guangzhou.

* Bydd pecyn yn cael ei anfon fel "rhodd" ac yn declear cyn lleied â phosib, nid oes angen i'r prynwr dalu am "TRETH".

* Ar ôl llong, byddwn yn anfon e-bost atoch a rhowch y rhif olrhain i chi.

|

|

|

Am Warant.

Cysylltwch â'r UD --- >> Dychwelwch yr eitem atom --- >> Derbyn ac anfon un arall yn ei lle.

Enw: Liu xiaoxia

Cyfeiriad: 305Fang HuiLanGe HuangPuDaDaoXi 273Hao TianHeQu Guangzhou Tsieina.

ZIP: 510620

Ffôn: + 8618078869184

Dychwelwch i'r cyfeiriad hwn ac ysgrifennu eich cyfeiriad paypal, enw, problem ar nodyn: |

|